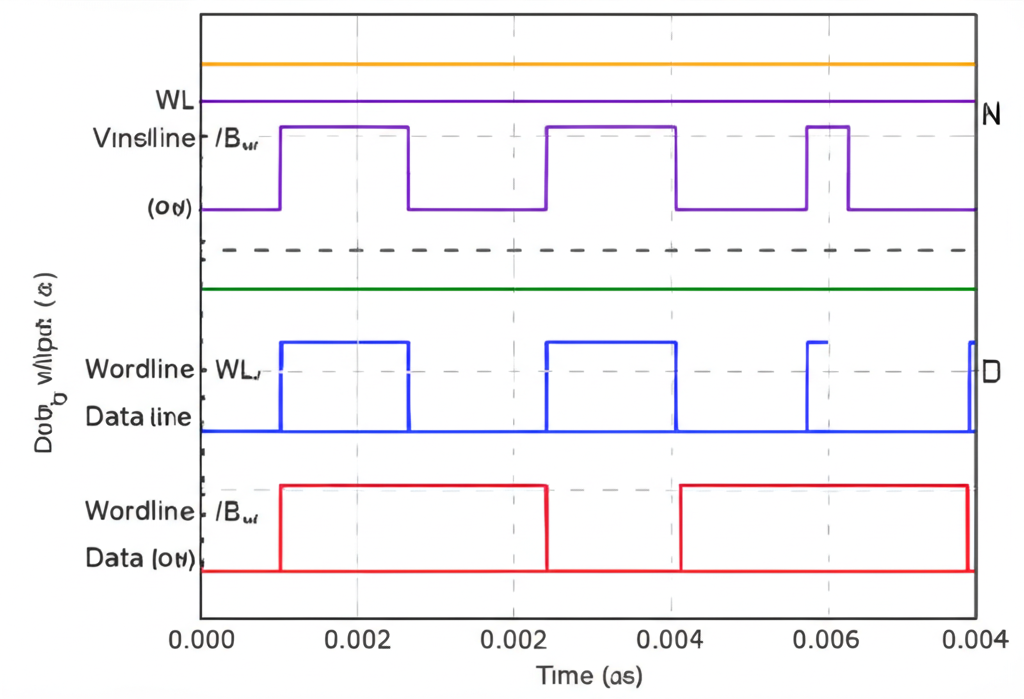

SPICE Simulation Results

Waveforms and test patterns for the NBA⁺ SRAM implementation

Write Operation SPICE Simulation

Waveform analysis of the SRAM cell during write operation

Write Operation Analysis

Signal Description:

| Signal | Description | Timing |

|---|---|---|

| WL (Wordline) | Activates the selected row of cells. When high, it connects the cell to the bitlines. | Activated at t=10ns, deactivated at t=30ns |

| BL (Bitline) | Carries the data value to be written (logic 1 in this case) | Driven high at t=5ns, before wordline activation |

| BLB (Bitline Bar) | Carries the complementary data value (logic 0 in this case) | Driven low at t=5ns, before wordline activation |

| Q (Cell Node) | Internal storage node of the SRAM cell | Transitions from 0 to 1 during write operation |

| QB (Cell Node Bar) | Complementary internal storage node | Transitions from 1 to 0 during write operation |

Key Observations:

- Write time: ~5ns from wordline activation to stable cell state

- Cell flips state when wordline is activated, allowing bitlines to overpower cell

- Write driver maintains stable bitline voltages throughout the operation

- Cell maintains new value after wordline is deactivated, demonstrating successful write

- Power consumption peaks during cell state transition

SPICE Simulation Parameters:

* SRAM Write Operation Simulation

.include "45nm_PTM.txt"

.param supply=1.0

.param temp=27C

.option post

.tran 0.01n 50n

.measure tran write_time trig v(WL) val=0.5 rise=1 targ v(Q) val=0.5 rise=1

Advanced SRAM Analysis

View detailed corner analysis, temperature effects, SNM, and power consumption data